# 3.0V to 5.5V RS485/RS422 Transceiver with ±15kV ESD Protection

## 1. Features

# High-Performance and Compliant with RS-485 EIA/ TIA-485 Standard

- High-Speed Data Rates: 20Mbps

- 1/8 Unit Load Enables up to 256 Nodes on the Same Rus

## • Integrated Protection for Robust Communication

- ±30V Fault Protection Range on Driver Outputs/Receiver Inputs

- ±15V Common-Mode Voltage Range

- ±15kV Human Body Model ESD Protection on the Bus Lines

- Hot-Swap Input Eliminates False Transitions during Power-up or Power-down

- Short-Circuit Protection

- Thermal Shutdown

- True Fail-Safe Guarantees Known Receiver Output State

## Low Power

- 960μA (max.) @ Receive Mode

- Shutdown Current < 5µA

- 3.0V to 5.5V Supply Voltage Range

- Wide Operating Temperature Range: -40°C to 125°C

- 14 pin SOIC Package

## 2. Applications

- Motor Driver

- Industrial Automation and Control

- Power Grid Infrastructure

- Building Automation

- HVAC System

- Video Surveillance

- Process Control

- Wireless Infrastructure

# 3. Description

The CA-IF4220NF is low-power, full-duplex transceiver for RS-485/RS-422 communications in harsh environments. This device features ±30V fault protection for overvoltage conditions on the bus lines that ensure robust protection for the communication interface. It also has ±15V wide common-mode range (CMR), this feature was specifically

designed for systems where there is a large common-mode voltage present due to either nearby electrically noisy equipment or large ground differences due to different grounds or long-distance transmission. The bus pins are protected against ±15kV electro-static discharge (ESD) shocks, eliminating the need for additional system level protection components.

The CA-IF4220NF contains one driver (TX) and one receiver (RX), operates over the +3.0V to +5.5V supply range, making it convenient for designers to use one part with either +3.3V or +5.0V supply systems. The CA-IF4220NF can transmit and receive at data rate up to 20Mbps. It also includes fail-safe circuitry, guaranteeing a logic-high receiver output when the receiver inputs are shorted or open.

The CA-IF4220NF is specified over the -40°C to +125°C wide operating temperature range and is available in 14-pin SOIC package for industry drop-in compatibility.

## **Device Information**

| Part Number | nber Package Package Size (Nom |                |  |  |

|-------------|--------------------------------|----------------|--|--|

| CA-IF4220NF | SOIC14                         | 3.9mm x 8.65mm |  |  |

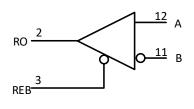

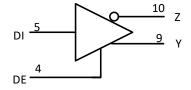

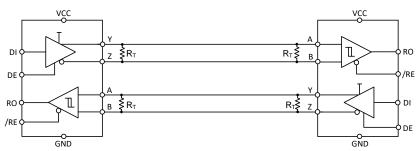

# **CA-IF4220NF Simplified Schematic Diagram**

# 4. Ordering Information

**Table 4-1. Ordering Information**

| Part # Full/Half-Duplex |             | Data Rate (Mbps) | Number of Nodes on Bus | Package     |  |

|-------------------------|-------------|------------------|------------------------|-------------|--|

| CA-IF4220NF             | Full duplex | 20               | 256                    | 14-pin SOIC |  |

# **Contents**

| 1. | Feat  | ures                                  | 1 |

|----|-------|---------------------------------------|---|

| 2. | Appl  | lications                             | 1 |

| 3. | Desc  | ription                               | 1 |

| 4. | Orde  | ering Information                     | 2 |

| 6. | Pin ( | Configuration and Descriptions        | 4 |

| 7. | Spec  | ifications                            | 5 |

|    | 7.1.  | Absolute Maximum Ratings <sup>1</sup> | 5 |

|    | 7.2.  | ESD Ratings                           | 5 |

|    | 7.3.  | Recommended Operating Conditions      | 5 |

|    | 7.4.  | Thermal Information                   | 5 |

|    | 7.5.  | Electrical Characteristics            | 6 |

|    | 7.6   | Switching Characteristics             | 7 |

|     | 7.7. | Typical Characteristics                | 8   |

|-----|------|----------------------------------------|-----|

| 8.  | Par  | ameter Measurement Information         | .12 |

| 9.  | Det  | ailed Description                      | .13 |

|     | 9.1. | Overview                               | 13  |

|     | 9.2. | Device Functional Modes                | 13  |

| 10. |      | Application Information                | .14 |

| 11. |      | Package Information                    | .15 |

| 12. |      | Soldering Temperature (reflow) Profile | .16 |

| 13. |      | Tape and Reel Information              | .17 |

| 14. |      | Important Statement                    | .18 |

# 5. **Revision History**

| Revision Number | Description | Page Changed |

|-----------------|-------------|--------------|

| Version 1.00    | N/A         | N/A          |

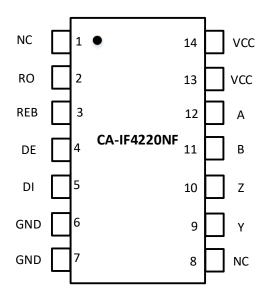

# 6. Pin Configuration and Descriptions

Figure 6-1. CA-IF4220NF pin configuration

Table 6-1. CA-IF4220NF pin description

| Pin Name        | Pin Number | Description                                                                                                         |

|-----------------|------------|---------------------------------------------------------------------------------------------------------------------|

| RO              | 2          | Receiver data output. With REB low, RO is high when $(V_A - V_B) > V_{TH+}$ and is low when $(V_A - V_B) < V_{TH+}$ |

| KO              | 2          | V <sub>TH</sub> RO is high impedance when REB is high.                                                              |

|                 |            | Receiver output enable. Drive REB low or connect to GND to enable RO. Drive REB high to                             |

| REB             | 3          | disable the receiver and put RO in high impedance. Drive REB high and DE low to force the IC                        |

|                 |            | into low-power shutdown mode.                                                                                       |

| DF              | 4          | Driver output enable. Drive DE high to enable the driver. Drive DE low or connect to GND to                         |

| DL              | 7          | disable the driver. Drive REB high and DE low to force the IC into low-power shutdown mode.                         |

|                 |            | Driver data input. With DE high, a logic low on DI forces the noninverting output (Y) low and the                   |

| DI              | 5          | inverting output (Z) high; a logic high on DI forces the noninverting output high and the                           |

|                 |            | inverting output low.                                                                                               |

| GND             | 6, 7       | Ground.                                                                                                             |

| Υ               | 9          | Noninverting RS-485/RS-422 driver output.                                                                           |

| Z               | 10         | Inverting RS-485/RS-422 driver output.                                                                              |

| В               | 11         | Inverting RS-485/RS-422 receiver input.                                                                             |

| А               | 12         | Noninverting RS-485/RS-422 receiver input.                                                                          |

| NC              | 1, 8       | No Connection. Not internally connected.                                                                            |

| V <sub>cc</sub> | 13, 14     | Power supply input. Bypass $V_{CC}$ to GND with at least $0.1\mu F$ capacitor as close to the device as possible.   |

# 7. Specifications

# 7.1. Absolute Maximum Ratings<sup>1</sup>

|                  | Parameters                     | Min  | Max                  | Unit |

|------------------|--------------------------------|------|----------------------|------|

| V <sub>CC</sub>  | Power supply voltage           | -0.3 | 7.0                  | V    |

| V <sub>IO</sub>  | Voltage at A, B, Z, Y          | -30  | 30                   | V    |

| V <sub>IO</sub>  | Voltage at DI, DE, REB         | -0.3 | 7.0                  | V    |

| V <sub>IO</sub>  | Voltage at RO                  | -0.3 | V <sub>CC</sub> +0.3 | V    |

| T <sub>J</sub>   | Operating junction temperature |      | 150                  | °C   |

| T <sub>STG</sub> | Storage temperature range      | -65  | 150                  | °C   |

## Note:

# 7.2. ESD Ratings

|                                          | Parameters Parameters Parameters                                           |     |    |

|------------------------------------------|----------------------------------------------------------------------------|-----|----|

|                                          | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, bus pin <sup>1</sup>   | ±15 | kV |

| V <sub>ESD</sub> Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, other pin <sup>1</sup> | ±6  | kV |

|                                          | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins  | ±2  | kV |

|                                          | ·                                                                          |     |    |

## Notes:

- 1. Per JEDEC document JEP155, 500V HBM allows safe manufacturing of standard ESD control process.

- 2. Per JEDEC document JEP157, 250V CDM allows safe manufacturing of standard ESD control process.

# 7.3. Recommended Operating Conditions

|                   | Parameters                     | Min | Тур | Max             | Unit |

|-------------------|--------------------------------|-----|-----|-----------------|------|

| V <sub>CC</sub>   | Analog power supply            | 3   | 5   | 5.5             | V    |

| V <sub>IN</sub>   | Input voltage at bus terminal  | -15 |     | 15              | V    |

| V <sub>IL</sub>   | Low-level input voltage        | 0   |     | 0.8             | V    |

| V <sub>IH</sub>   | High-level input voltage       | 2   |     | V <sub>CC</sub> | V    |

| R <sub>L</sub>    | Differential load resistance   | 54  |     |                 | Ohm  |

| 1/t <sub>UI</sub> | Data rate                      |     |     | 20              | Mbps |

| T <sub>A</sub>    | Ambient temperature            | -40 |     | 125             | °C   |

| TJ                | Operating junction temperature | -40 |     | 150             | °C   |

# 7.4. Thermal Information

| Thermal Metric                                         | CA-IF4220NF<br>SOIC14 | Unit |

|--------------------------------------------------------|-----------------------|------|

| $R_{\theta JA}$ Junction-to-ambient thermal resistance | 120                   | °C/W |

<sup>1.</sup> The stresses listed under "Absolute Maximum Ratings" are stress ratings only, not for functional operation condition. Exposure to absolute maximum rating conditions for extended periods may cause permanent damage to the device.

# 7.5. Electrical Characteristics

All typical specs are at VCC = 5V, TA = 25°C, Min/Max specs are over recommended operating conditions unless otherwise specified.

|                     | Parameters                                      | Test Condition                                                | ıs                         | Min                  | Тур                  | Max      | Unit                 |

|---------------------|-------------------------------------------------|---------------------------------------------------------------|----------------------------|----------------------|----------------------|----------|----------------------|

| Driver              |                                                 |                                                               |                            |                      |                      |          |                      |

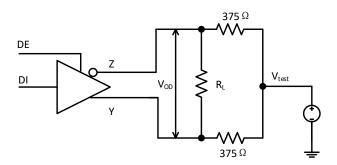

|                     |                                                 | $R_L = 60\Omega$ , $-15V \le V_{test} \le 15V$                | / (See                     | 1.5                  | _                    |          | T ,,                 |

|                     |                                                 | Figure 8-1) <sub>(1)</sub>                                    | Figure 8-1) <sub>(1)</sub> |                      | 3.5                  |          | V                    |

| Iv. I               | Differential autority altern                    | $R_L = 60\Omega$ , $-15V \le V_{test} \le 15V$                | Ι,                         | 2.1                  |                      |          |                      |

| V <sub>OD</sub>     | Differential-output voltage                     | 4.5V≤V <sub>CC</sub> ≤5.5V (See Figu                          | ure 8-1)                   | 2.1                  |                      |          |                      |

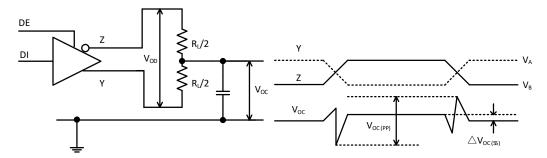

|                     |                                                 | R <sub>L</sub> =100Ω (See Figure 8-2                          | 2)                         | 2                    | 4                    |          | V                    |

|                     |                                                 | R <sub>L</sub> =54Ω (See Figure 8-2)                          |                            | 1.5                  | 3.7                  |          | V                    |

| Δ V <sub>OD</sub>   | Change in differential-output voltage           | $R_L$ =54 $\Omega$ (See Figure 8-2)                           |                            | -200                 |                      | 200      | mV                   |

| Voc                 | Common-mode output voltage                      |                                                               |                            | 1                    | V <sub>cc</sub> /2   | 3        | V                    |

| ۸۱/                 | Change in steady-state common-mode output       | K <sub>L</sub> =54Ω (See Figure 8-2)                          |                            | -200                 |                      | 200      | m\/                  |

| $\Delta V_{OC(SS)}$ | voltage                                         |                                                               |                            | -200                 |                      | 200      | mV                   |

| I <sub>OS</sub>     | Short-circuit output current                    | -7V≤V <sub>0</sub> ≤12V                                       |                            | -250                 |                      | 250      | mA                   |

| Receiver            |                                                 |                                                               |                            |                      |                      |          |                      |

|                     |                                                 | DF-0\/ \/ -0\/ or F\/                                         | V <sub>I</sub> =12V        |                      | 75                   | 125      | uA                   |

| 1                   | Bus input current                               | DE=0V, V <sub>CC</sub> =0V or 5V                              | V <sub>I</sub> =-7V        | -100                 | -43                  |          | uA                   |

| I <sub>I</sub>      |                                                 | DE 01/1/ 01/2= E1/                                            | V <sub>I</sub> =15V        |                      | 91                   | 125      | uA                   |

|                     |                                                 | DE=0V, V <sub>CC</sub> =0V or 5V                              | V <sub>I</sub> =-15V       | -200                 | -97                  |          | uA                   |

| V <sub>TH+</sub>    | Receiver differential threshold voltage rising  |                                                               | •                          |                      | -100                 | -20      | mV                   |

| V <sub>TH-</sub>    | Receiver differential threshold voltage falling | Over common mode range                                        |                            | -200                 | -130                 |          | m۷                   |

| V <sub>HYS</sub>    | Receiver input hysteresis                       |                                                               |                            |                      | 30                   |          | mV                   |

| V <sub>OH</sub>     | High-level output voltage                       | I <sub>OH</sub> =-4mA                                         |                            | V <sub>CC</sub> -0.4 | V <sub>CC</sub> -0.2 |          | V                    |

| V <sub>OL</sub>     | Low-level output voltage                        | I <sub>OL</sub> =4mA                                          |                            |                      | 0.2                  | 0.4      | V                    |

| I <sub>OZR</sub>    | Output high-impedance current                   | V <sub>O</sub> =0V or V <sub>CC</sub> , REB at V <sub>C</sub> | C                          | -1                   |                      | 1        | uA                   |

| Input logic         |                                                 |                                                               |                            |                      |                      |          |                      |

| VIH                 | Logic-high input                                | DI, V <sub>CC</sub> =5.5V                                     |                            | 2                    |                      |          | V                    |

| VIL                 | Logic-low input                                 | DI, V <sub>CC</sub> =4.5V                                     |                            |                      |                      | 0.8      | V                    |

| I <sub>IN</sub>     | Logic input current                             | 3V≤V <sub>CC</sub> ≤5.5V, 0V≤V <sub>IN</sub> ≤V               | cc                         | -6.2                 |                      | 6.2      | uA                   |

| Device              |                                                 |                                                               |                            |                      |                      |          |                      |

|                     |                                                 | Driver and receiver ena                                       | bled,                      | 0.4                  | 0.0                  | 1.2      |                      |

|                     |                                                 | REB=0V, DE = $V_{CC}$ , no los                                | ad                         | 0.4                  | 0.8                  | 1.2      | mA                   |

|                     |                                                 | Driver enabled, receive                                       | disabled,                  |                      | 0.8                  | 1.2      | mA                   |

| i                   | Supply current (quiescent)                      | REB= $V_{CC}$ , DE = $V_{CC}$ , no load                       |                            |                      | 0.8                  | 1.2      | IIIA                 |

| I <sub>CC</sub>     | Supply culterit (quiescellt)                    | Driver disabled, receiver enabled,                            |                            |                      | 700                  | 060      | 11.0                 |

|                     |                                                 | REB=0V, DE = 0V, no load                                      |                            |                      | 700                  | 960      | uA                   |

|                     |                                                 | Driver disabled, receiver disabled,                           |                            | d,                   | 2.4                  | 5        | uA                   |

|                     |                                                 | REB= $V_{CC}$ , DE = 0V, D=op                                 | en, no load                |                      | ۷.4                  | <u> </u> |                      |

| T <sub>SD</sub>     | Thermal shutdown temperature                    |                                                               |                            |                      | 180                  |          | $^{\circ}\mathbb{C}$ |

#### Notes:

- 1.  $|V_{OD}| \ge 1.4 \text{ V}$  with  $T_A > 85^{\circ}\text{C}$ ,  $V_{test} < -7 \text{ V}$  and  $V_{CC} < 3.135 \text{ V}$ .

- 2. Under any condition, ensure that  $V_{\text{TH+}}$  is at least  $V_{\text{HYS}}$  higher than  $V_{\text{TH-}}$

# 7.6. Switching Characteristics

All typical specs are at VCC = 5V,  $T_A$  = 25°C, Min/Max specs are over recommended operating conditions unless otherwise specified.

|                                    | Parameters                                       | Test Conditions                                          | Min | Тур | Max | Unit |

|------------------------------------|--------------------------------------------------|----------------------------------------------------------|-----|-----|-----|------|

| Driver                             |                                                  |                                                          |     |     |     |      |

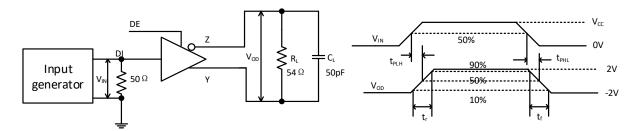

| t <sub>r</sub> , t <sub>f</sub>    | Driver differential output rise/fall time        | $R_1$ =54 Ω, $C_1$ =50pF, Figure 8-3                     | 1   | 3   | 6   | ns   |

| t <sub>PHL</sub> ,t <sub>PLH</sub> | Propagation delay                                | - κ <sub>L</sub> -54 Ω, C <sub>L</sub> -50με, Figure 6-5 | 3   | 10  | 20  | ns   |

| t <sub>SK(P)</sub>                 | Pulse skew,  t <sub>PHL</sub> - t <sub>PLH</sub> |                                                          |     |     | 3.5 | ns   |

| Receiver                           |                                                  |                                                          |     |     |     |      |

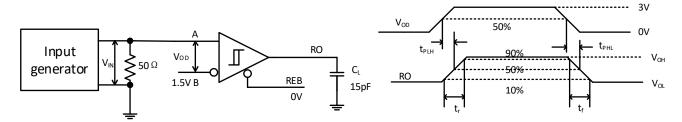

| t <sub>r</sub> , t <sub>f</sub>    | Output rise/fall time                            |                                                          |     | 2   | 6   | ns   |

| t <sub>PHL</sub> ,t <sub>PLH</sub> | Propagation delay                                | C <sub>L</sub> =15pF, see Figure 8-4                     |     | 25  | 40  | ns   |

| t <sub>SK(P)</sub>                 | Pulse skew,  t <sub>PHL</sub> - t <sub>PLH</sub> |                                                          |     |     | 3.5 | ns   |

# CHIPANALOG

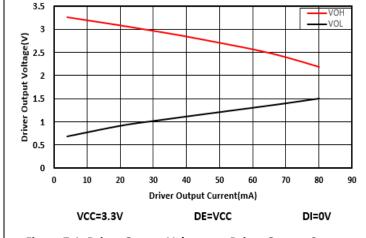

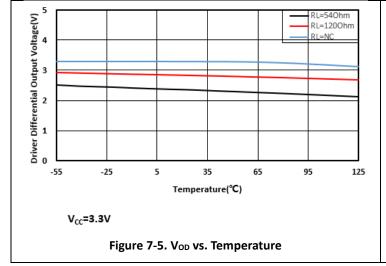

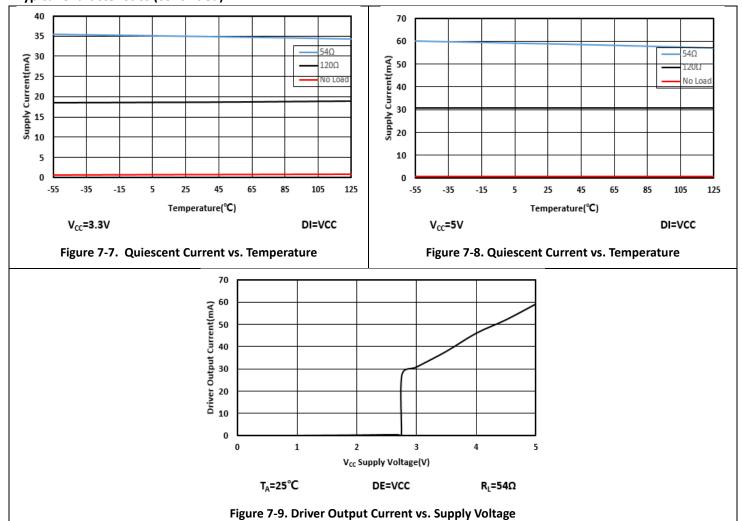

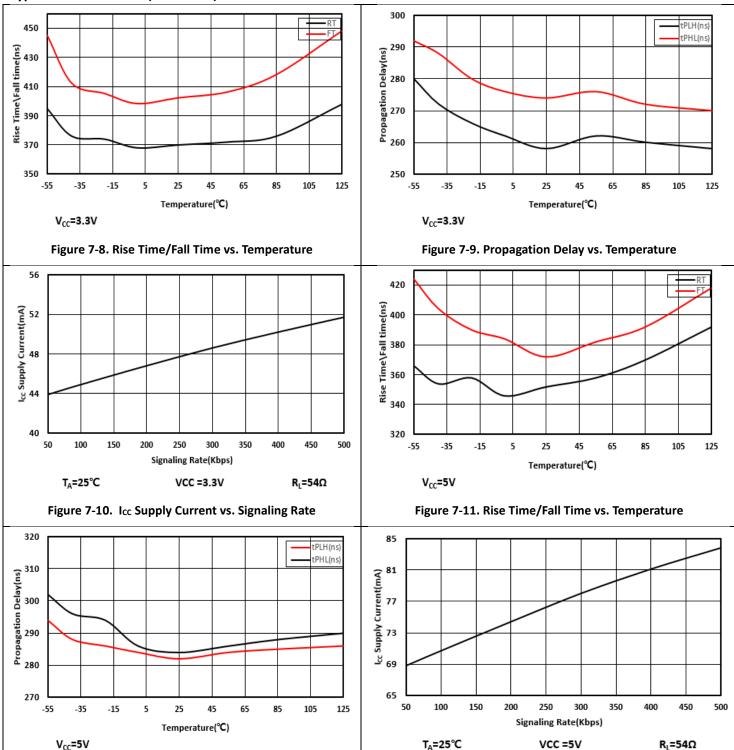

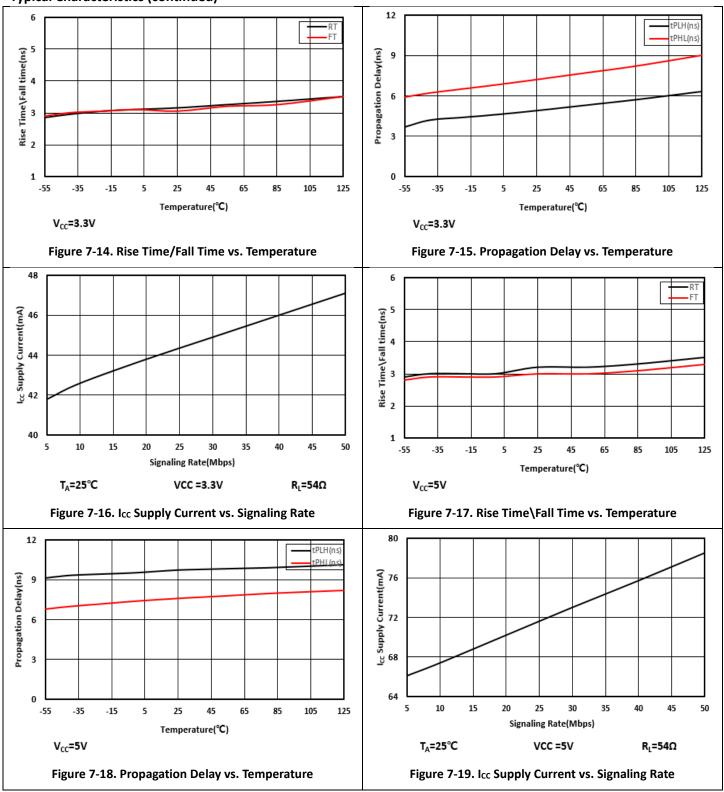

# 7.7. Typical Characteristics

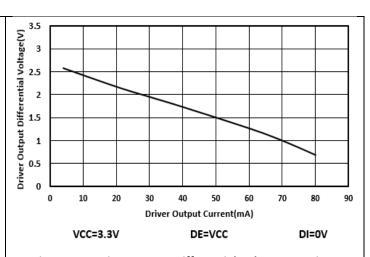

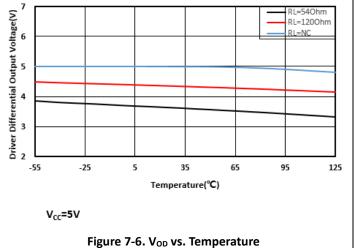

Figure 7-1. Driver Output Voltage vs. Driver Output Current

Figure 7-2. Driver Output Differential Voltage vs. Driver Output Current

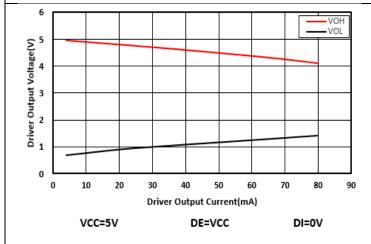

Figure 7-3. Driver Output Voltage vs. Driver Output Current

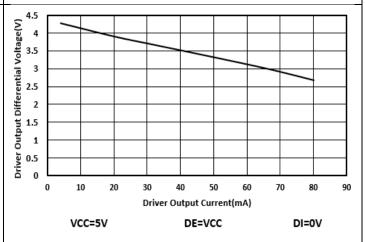

Figure 7-4. Driver Output Differential Voltage vs. Driver Output Current

# **Typical Characteristics (continued)**

Figure 7-13. Icc Supply Current vs. Signaling Rate

# CHIPANALOG

# **Typical Characteristics (continued)**

Figure 7-12. Propagation Delay vs. Temperature

# **Typical Characteristics (continued)**

Shanghai Chipanalog Microelectronics Co., Ltd.

# 8. Parameter Measurement Information

Figure 8-1. Driver Differential Output Voltage with Common-Mode Load

Figure 8-2. Driver Differential and Common-Mode Output with RS-485 Load

Figure 8-3. Driver Differential Output Rise and Fall Times and Propagation Delays

Figure 8-4. Receiver Output Rise and Fall Times and Propagation Delays

## 9. Detailed Description

#### 9.1. Overview

The CA-IF4220NF device is optimized for full-duplex RS-485/RS-422 applications per the EIA/TIA-485 standard. This device contains one differential driver and one differential receiver. The receiver features a 1/8-unit load input impedance, allowing up to 256 transceivers on a single bus. Driver-enable (DE) and receiver-enable (REB) pins are included on the CA-IF4220NF transceivers. When disabled, the driver and receiver outputs are high impedance.

To reduce system complexity and the need for external protection, the driver outputs/receiver inputs of the CA-IF4220NF device are designed to withstand voltage faults of up to ±30V with respect to ground without damage, and the common-mode range exceeds the standard with ±15V for both the driver and receiver. This device also incorporates a high ESD protection circuit capable of protecting against up to ±15kV of ESD Human Body Model (HBM) for driver outputs and receiver inputs. In addition, two mechanisms against excessive power dissipation caused by faults or bus contention. The first, over-current protection on the output stage, provides immediate protection against short circuits over the entire common-mode voltage range. The second, a thermal shutdown circuit, forces the driver outputs into a high-impedance state once the junction temperature of the device exceed the thermal shutdown threshold T<sub>SD</sub> (180°C, typ.). The shutdown condition is cleared when the junction temperature drops to normal operation temperature range of the device.

## 9.2. Device Functional Modes

For the CA-IF4220NF full-duplex device, the driver accepts a single-ended, logic-level input (DI) and transfers it to a differential RS-485/RS-422 level output on the Y and Z bus lines. Set the driver enable input (DE) low to disable the driver. Y and Z are high impedance when the driver is disabled. Also, the DE pin has internal pull-down to GND, when left open, the driver is disabled as well. The DI pin has an internal pull-up resistor to  $V_{CC}$ , thus, when DI left open or a logic high at DI causes Y to turn high and Z to turn low. When DI is low, the output states reverse, Z turns high, Y becomes low. See Table 9-1 for more details.

| Input                  | Enable                    | Output               |   | Function                   |

|------------------------|---------------------------|----------------------|---|----------------------------|

| DI                     | DE                        | Υ                    | Z | Function                   |

| Н                      | Н                         | Н                    | L | Drive bus high             |

| L                      | Н                         | L H Di               |   | Drive bus low              |

| Χ                      | L                         | Z                    | Z | Driver disabled            |

| Χ                      | OPEN                      | Z                    | Z | Driver disabled by default |

| OPEN                   | Н                         | Н                    | L | Drive bus high by default  |

| Note:                  |                           |                      |   |                            |

| L = Low level; H = Hig | gh level; Z = high impeda | nce; X = Don't care. |   |                            |

Table 9-1. CA-IF4220NF Driver Function Table

The receiver accepts a differential, RS-485/RS-422 level input on the A and B inputs and transfers it to a single-ended, logic-level output (RO). Drive the receiver enable input (REB) low to enable the receiver. Drive REB high to disable the receiver. RO is high impedance when REB is high. Also, the REB pin has an internal pull-up resistor to  $V_{CC}$ , thus, when left open, the receiver is disabled, and RO output is high impedance.

The CA-IF4220NF includes a true fail-safe feature that ensures the receiver output (RO) is high when the receiver inputs are shorted or open, or when they are connected to a differentially terminated transmission line with all drivers disabled. If the differential receiver input voltage ( $V_A - V_B$ ) is greater than or equal to  $V_{TH+}$  (-20mV, maximum), RO is logic high. When the input voltage ( $V_A - V_B$ ) is less than the negative input threshold  $V_{TH-}$  (-200mV, minimum), the receiver output RO turns low. See Table 9-2 for more details.

| Table 0.3 | CA-IE4220NE                             | Danairea | F at: a   | Table |

|-----------|-----------------------------------------|----------|-----------|-------|

| Ianie 4-7 | $(\Delta - I + \Delta J J I) I I I I I$ | ROCOIVOR | FIINCTION | IDNIA |

| Differential Input                                 | Enable | Output        | Function                     |

|----------------------------------------------------|--------|---------------|------------------------------|

| $V_{ID} = V_A - V_B$                               | REB    | RO            | FullCtion                    |

| $V_{TH+} < V_{ID}$                                 | L      | Н             | High-level bus state         |

| $V_{TH-} < V_{ID} < V_{TH+}$                       | L      | Indeterminate | Indeterminate bus state      |

| $V_{ID} < V_{TH}$                                  | L      | L             | Low-level bus state          |

| X                                                  | Н      | Z             | Receiver disabled            |

| X                                                  | OPEN   | Z             | Receiver disabled by default |

| Open-circuit bus                                   | L      | Н             | Fail-safe high output        |

| Short-circuit bus                                  | L      | Н             | Fail-safe high output        |

| Idle (terminated) bus                              | L      | Н             | Fail-safe high output        |

| Note:                                              | •      |               |                              |

| L = Low level; H = High level; Z = high impedance. |        |               |                              |

# 10. Application Information

The CA-IF4220NF full-duplex RS-485 transceivers commonly used for asynchronous data transmissions. A full-duplex network implementation requires two signal pairs (four wires) cable and allows each node to transmit data on one pair while simultaneously receiving data on the other pair, see Figure 错误!未找到引用源。 a typical point to point application circuit for CA-IF4220NF.

Figure 10-1. Typical Full-duplex Point to Point Operating Circuit

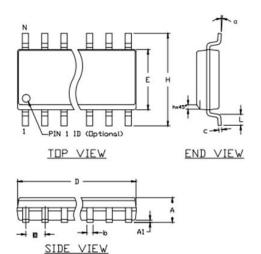

# 11. Package Information

# **SOIC14 Package Outline**

Shanghai Chipanalog Microelectronics Co., Ltd.

|        |      | COMMO   | N DIME | NSIONS   | 3     |      |  |

|--------|------|---------|--------|----------|-------|------|--|

| SYMBOL |      | INCHES  |        | ММ       |       |      |  |

| SIMBUU | MIN. | TYP.™   | MAX.   | MIN.     | TYP.™ | MAX. |  |

| Α      | .053 | .061    | .069   | 1.35     | 1.55  | 1.75 |  |

| A1     | .004 | .007    | .010   | 0.10     | 0.18  | 0.25 |  |

| b<br>c | .014 | .017    | .019   | 0.35     | 0.42  | 0.49 |  |

|        | .007 | .009    | .010   | 0.19     | 0.22  | 0.25 |  |

| E      | .150 | .154    | .157   | 3.80     | 3.90  | 4.00 |  |

| е      |      | 050 BSC |        | 1.27 BSC |       |      |  |

| Н      | .228 | .236    | .244   | 5.80     | 6.00  | 6.20 |  |

| L      | .016 | .033    | .050   | 0.40     | 0.84  | 1.27 |  |

| α      | 0*   | 4*      | 8*     | 0*       | 4*    | 8.   |  |

| h      | 0.01 | 0.015   | 0.019  | 0.25     | 0.38  | 0.5  |  |

\* Typical value provided for reference only. This is not a specification.

|              | VARIATION A      |                                                  |                     |                      |               |         |  |  |

|--------------|------------------|--------------------------------------------------|---------------------|----------------------|---------------|---------|--|--|

| SYMBOL       | INC              | HES                                              |                     | MM                   |               |         |  |  |

|              | MIN.             | TYP.*                                            | MAX.                | MIN.                 | TYP. <b>≖</b> | MAX.    |  |  |

| D            | .189             | .193                                             | .197                | 4.80                 | 4.90          | 5.00    |  |  |

| N            |                  |                                                  | 8                   |                      |               |         |  |  |

| MS012        | AA               |                                                  |                     |                      |               |         |  |  |

| PKG.<br>CODE | S8+8F,<br>S8+20, | \$8+2C, \$1<br>\$8+10F,<br>\$8+21, \$<br>\$8+23, | S8+11F,<br>8MK+1, S | \$8+16F,<br>8M+5, \$ | SS+2M8        | \$8+7F, |  |  |

|              |      | V                 | ARIATI | IN B |                   |      |  |  |  |

|--------------|------|-------------------|--------|------|-------------------|------|--|--|--|

| SYMBOL       | INC  | HES               |        | ММ   |                   |      |  |  |  |

|              | MIN. | TYP. <sup>™</sup> | MAX.   | MIN. | TYP. <sup>™</sup> | MAX. |  |  |  |

| D            | .337 | .341              | .344   | 8.55 | 8.65              | 8.75 |  |  |  |

| N            |      |                   | 1      | 4    |                   |      |  |  |  |

| MS012        | AB   |                   |        |      |                   |      |  |  |  |

| PKG.<br>CODE |      | S14+1C<br>4, S14M |        |      | 5, S14+6<br>14M+7 | ·,   |  |  |  |

|              |        | V     | ARIATI  | IN C |                    |       |  |  |  |  |

|--------------|--------|-------|---------|------|--------------------|-------|--|--|--|--|

| SYMBOL       | INC    | HES   |         | ММ   |                    |       |  |  |  |  |

|              | MIN.   | TYP.™ | MAX.    | MIN. | TYP.™              | MAX.  |  |  |  |  |

| D            | .386   | .390  | .394    | 9.80 | 9.90               | 10.00 |  |  |  |  |

| N            | 16     |       |         |      |                    |       |  |  |  |  |

| MS012        | AC     |       |         |      |                    |       |  |  |  |  |

| PKG.<br>CDDE | \$16+7 |       | 9F, S16 |      | 5, S16+6<br>16M+3, |       |  |  |  |  |

## NOTES:

- 1. ALL DIMENSIONS ARE IN MILLIMETERS UNLESS DTHERWISE SPECIFIED.

- 2. MATERIAL MUST COMPLY WITH BANNED AND RESTRICTED SUBSTANCES SPEC # 10-0131.

- DIMENSIONS D AND E DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE MOLD PROTRUSION IS 0.15 MM (.006') PER SIDE.

- 4. LEADS TO BE COPLANAR WITHIN 0.10mm (.004").

- 5. MEETS JEDEC MS012

- 6. ALL DIMENSIONS APPLY TO BOTH LEADED (-) AND PHEREE (+) PKG. CODES.

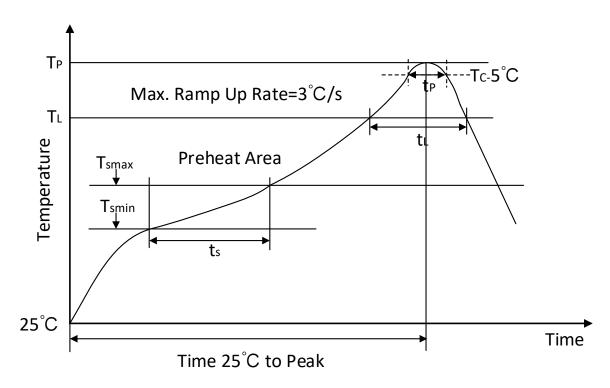

# 12. Soldering Temperature (reflow) Profile

Figure 12-1. Soldering Temperature (reflow) Profile

**Table 12-1. Soldering Temperature Parameter**

| Profile Feature                                                      | Pb-Free Assembly |

|----------------------------------------------------------------------|------------------|

| Average ramp-up rate (T <sub>L</sub> =217°C to peak T <sub>P</sub> ) | 3°C/s max        |

| Time of preheat temperature, 150°C to 200°C                          | 60-120s          |

| Time to be maintained above 217°C                                    | 60-150s          |

| Peak temperature                                                     | 260°C            |

| Time within 5°C of actual peak temperature                           | 30s max          |

| Ramp-down rate (peak T <sub>P</sub> to T <sub>L</sub> =217°C)        | 6°C/s max        |

| Time from 25 ℃ to peak temperature                                   | 8min max         |

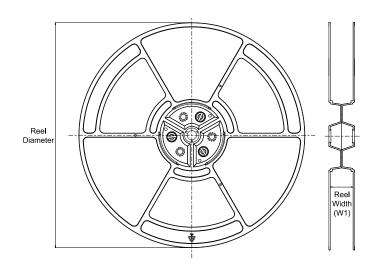

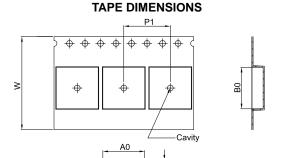

# 13. Tape and Reel Information

# **REEL DIMENSIONS**

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

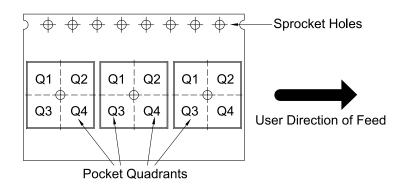

# **QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device      | Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|------|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| CA-IF4220NF | SOIC            | NF                 | 14   | 2500 | 330                      | 16.4                     | 6.5        | 9.0        | 2.1        | 8.0        | 16.0      | 01               |

## 14. Important Statement

The above information is for reference only and used for helping Chipanalog customers with design, research and development. Chipanalog reserves the rights to change the above information due to technological innovation without advance notice.

All Chipanalog products pass ex-factory test. As for specific practical applications, customers need to be responsible for evaluating and determining whether the products are applicable or not by themselves. Chipanalog's authorization for customers to use the resources are only limited to development of the related applications of the Chipanalog products. In addition to this, the resources cannot be copied or shown, and Chipanalog is not responsible for any claims, compensations, costs, losses, liabilities and the like arising from the use of the resources.

## **Trademark information**

Chipanalog Inc.® and Chipanalog® are registered trademarks of Chipanalog.

http://www.chipanalog.com